Taktgesteuerte Flipflops

https://bildung.social/@oerinformatik/113759982270606588

https://oer-informatik.de/flipflops_taktgesteuert

tl/dr; (ca. 8 min Lesezeit): Flipflops sind flexibler einsetzbar, wenn man mit einem Takt einen weiteren Eingang anfügt. Es wird Taktzustands- und Taktflankensteuerung unterschieden - beide lasse sich jeweils negieren oder durch taktunabhängige Eingänge ergänzen. Die Königsdiziplin ist das zweitaktflankengesteuerte Flipflop. Kleine Übungsaufgaben sind in den Text integriert. (Zuletzt geändert am 06.01.2025)

Teil der Serie zu Flipflopschaltungen: Grundlagen, Taktsteuerung, D-/T-/JK-Flipflops

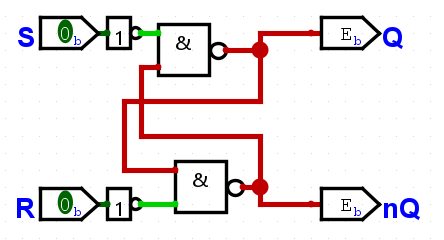

RS-Flipflop mit Taktzustandssteuerung

Bei komplexeren Schaltungen aus mehreren Flipflops und Logikgattern soll sichergestellt werden, dass zu bestimmten Zeitpunkten die Eingangssignale ausgewertet werden. Hierzu wird das RS-Flipflop um einen weiteren Eingang ergänzt: der Takt, englisch: Clock, daher trägt der Eingang die Bezeichnung C. Nur wenn an diesem Eingang eine 1 anliegt, werden die Eingangssignale R und S ausgewertet - dies wird über zwei AND-Gatter realisiert:

Man spricht in diesem Fall von einem taktzustandsgesteuerten Flipflop. Das Schaltzeichen weist den Takt (C1) und die taktabhängigen Eingänge aus (1R, 1S). Auf integrierten Schaltkreisen (ICs) sind häufig mehrere Flipflops mit jeweils eigenen Takteingängen verbaut - die jeweilige Nummer der Eingänge weist den zugehörigen Takt zu, von denen der Eingang abhängig ist.

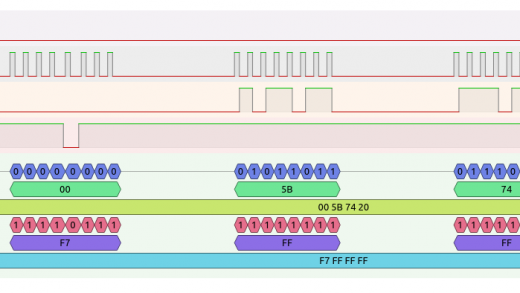

Das Impulsdiagramm veranschaulicht die Wirkungsweise der Taktzustandssteuerung: nur wenn am Taktsignal ein high anliegt, werden die Steuersignale weitergeleitet. In allen grau eingezeichneten Bereichen ist das Taktsignal low und folglich ändert sich der Flipflop-Zustand nicht.

Übungsaufgabe: Welchen Zustand hat das oben abgebildete taktzustandsgesteuerte RS-Flipflop am Ausgang Q bei folgenden Eingangssignalen? Zu Beginn ist der Zustand des Flipflop-Ausgangs unbestimmt.

Bei der folgenden Lösung wurden Eingangssignale, die eine Zustandsänderung hervorrufen, gesondert markiert:

Interessant ist hierbei das Verhalten unmittelbar beim 2. und 3. Takt: die Eingangssignale haben sich bei low-Pegel des Takts geändert, das Flipflop schaltet aber erst, sobald die Clock auf high springt.

Natürlich kann der Takt ebenso wie alle anderen Eingangssignale auch negiert genutzt werden - die Verarbeitung der Eingangssignale erfolgt dann beim Taktzustand 0. Das Schaltzeichen wird durch einen Negierungskreis am Eingang des Taktes erweitert:

Übungsaufgabe: Selbstverständlich ändert sich bei negiertem Takt auch das Verhalten des Flipflops grundlegend. Lassen wir es auf einen Versuch ankommen: nehmen wir an, es liegen exakt die gleichen Eingangssignale vor, wie bei dem Beispiel oben: welchen Zustand hat das negativ-taktzustandsgesteuerte RS-Flipflop am Ausgang Q bei folgenden Eingangssignalen?

Bei der folgenden Lösung wurden Eingangssignale, die eine Zustandsänderung hervorrufen, gesondert markiert:

In einigen Fällen ist es wünschenswert, dass es neben den taktzustandsabhängigen Eingängen R und S auch noch Eingänge gibt, die (wie bei einem einfachen RS-Flipflop) auch ohne Taktsignal das Flipflop schalten können. Diese Eingänge werden Preset oder PRE (für ein taktunabhängiges Setzen) und Clear oder CLR (für ein taktunabhängiges Rücksetzen) genannt. In Logik-Simulationssoftware wird für diese Eingänge häufig die führende Zahl weggelassen, die andeutet, wenn Eingänge taktabhängig sind. Auf konkreten ICs sind diese Zahlen jedoch i.d.R. vorhanden, um zuordnen zu können, zu welchem Flipflop die Eingänge gehören.

Übungsaufgabe: Taktunabhängige Eingänge einfügen kann nicht so schwer sein, oder? Erweitere dieses taktgesteuerte Flipflop (LogiJS-Link) um die beiden taktunabhängigen Eingänge Preset und Clear:

Wenn die Schaltung um zwei OR-Gatter vor den Eingängen ergänzt werden, die jeweils das taktabhängige und taktunabhängige Signal zusammenfassen, dann ist die gewünschte Funktionalität erreicht:

Hinweis: in gängigen ICs sind die taktunabhängigen Eingänge häufig negiert ausgeführt: \overline{PRE} (nicht-Preset) und \overline{CLR} (nicht-Clear) - das heißt, beide Eingänge werden normalerweise auf high (1) gelegt und nur für taktunabhäniges Schalten kurzzeitig mit low (0) beschaltet.

Übungsaufgabe: Welchen Zustand hat das oben abgebildete taktzustandsgesteuerte RS-Flipflop am Ausgang Q bei folgenden Eingangssignalen? Zu Beginn ist der Zustand des Flipflop-Ausgangs unbestimmt.

Bei der folgenden Lösung wurden Eingangssignale, die eine Zustandsänderung hervorrufen, gesondert markiert:

Interessant ist hierbei das Verhalten unmittelbar beim 2. und 3. Takt: die Eingangssignale haben sich bei low-Pegel des Takts geändert, das Flipflop schaltet aber erst, sobald die Clock auf high springt.

RS-Flipflop mit Taktflankensteuerung

Ein Problem der Taktzustandssteuerung ist, dass ein Flipflop während eines Takts mehrmals den Zustand wechseln kann - nämlich solange, wie der Taktzustand high ist. Im obigen Impulsdiagramm wechselt der Zustand des Flipflops beispielsweise im Takt 5 mehrmals.

Bei komplexeren Schaltungen mit vielen Bauteilen und längeren Signallaufzeiten kann dies zu Problemen führen, da sich innerhalb eines Taktes auch die Eingangssignale des Flipflops verändern können. Es wäre daher wünschenswert, die Schaltung so anzupassen, dass sich in jedem Takt der Zustand des Flipflops nur genau einmal ändern kann.

Erreicht wird dies durch die Taktflankensteuerung: die Schaltung wird so angepasst, dass nicht mehr der Zustand des Takts die Eingänge durchschaltet, sondern eine Zustandsänderung: also einer Flanke des Taktsignals.

Mit unseren Grund-Logikgattern (AND, OR, NOT) können wir nur Zustände auswerten, aber keine Zustandsänderungen. Man hilft sich mit einem kleinen Trick: jedes (reale) Logikgatter benötigt eine gewisse Signallaufzeit, bis die Eingangssignaländerung am Ausgang anliegt. Wird bei einer Negierung das Eingangs- und Ausgangssignal betrachtet, so sind beim Zustandswechsel des Eingangs auf high für einen kurzen Augenblick (eine Signallaufzeit lang) Ausgangs- und Eingangssignal high. Werden diese AND-verknüpft ist sichergestellt, dass das Flipflop nur für einen kurzen Augenblick Zustandsänderungen durchführt.

Häufig ist die Signallaufzeit in Simulationsprogrammen so gering, dass mehrere Negierungen hintereinander geschaltet werden müssen, um eine funktionierende Flankenerkennung zu erhalten. Mit einer ungeraden Anzahl an Negierungen reagiert das Flipflop auf eine steigende (positive) Taktflanke, mit einer geraden Anzahl an Negierungen reagiert es auf eine sinkende (negative) Taktflanke.

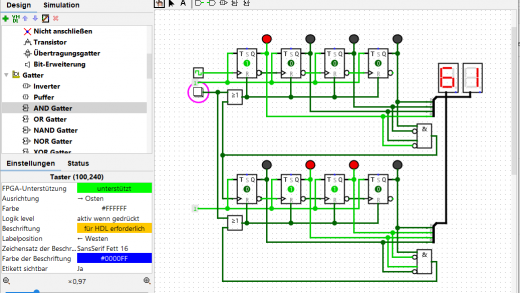

Im Fall von Logisim ist die Laufzeit von drei Invertierern nötig, um ein taktflankengesteuertes Flipflop aufzubauen:

Als Schaltzeichen wird am Takteingang (Clock) ein Dreieck notiert, was die Flankensteuerung symbolisieren soll:

Übungsaufgabe: Welchen Zustand hat das oben abgebildete taktflankengesteuerte RS-Flipflop am Ausgang Q bei folgenden Eingangssignalen? Zu Beginn ist der Zustand des Flipflop-Ausgangs unbestimmt - als kleine erste Hilfestellung sind die relevanten positiven Taktflanken gelb markiert:

Bei der folgenden Lösung wurden Eingangssignale, die eine Zustandsänderung hervorrufen, gesondert markiert:

Interessant ist hierbei das Verhalten unmittelbar beim 2. und 3. Takt: die Eingangssignale haben sich bei low-Pegel des Takts geändert, das Flipflop schaltet aber erst, sobald die Clock auf high springt.

Wenn das Flipflop auf fallende Flanken reagiert (also eine gerade Anzahl an Negierungen ins Taktsignal eingebunden sind) wird dies im Schaltzeichen durch eine Negierung vor dem Flanken-Dreieck an der Clock notiert:

Übungsaufgabe: Welchen Zustand hat das oben abgebildete negiert-taktflankengesteuerte RS-Flipflop am Ausgang Q bei folgenden Eingangssignalen? Zu Beginn ist der Zustand des Flipflop-Ausgangs unbestimmt - als kleine erste Hilfestellung sind die relevanten fallenden Taktflanken gelb markiert:

Bei der folgenden Lösung wurden Eingangssignale, die eine Zustandsänderung hervorrufen, gesondert markiert:

Interessant ist hierbei das Verhalten unmittelbar beim 2. und 3. Takt: die Eingangssignale haben sich bei low-Pegel des Takts geändert, das Flipflop schaltet aber erst, sobald die Clock auf high springt.

Zwei-Taktflankensteuerung: die MS-Flipflops

Anders als es vielleicht der Name erwarten lässt, reagiert ein zwei-taktflankengesteuertes Flipflop nicht einfach auf beide Flanken gleichermaßen. Vielmehr haben die beiden Flanken unterschiedliche Bedeutungen, denn diese Art Flipflop besteht aus zwei einzelnen Flipflops, das erste reagiert auf die steigende Taktflanke, das zweite auf die fallende Taktflanke. Die beiden inneren Flipflops trugen früher die Bezeichnung master / slave, daher stammt die Bezeichnung MS-Flipflop. Heute tendiert man zu weniger belasteten Begriffen, die Aufteilung main / steward gibt etwa die Funktionen wieder (und ermöglichen, weiterhin von “MS-Flipflops” zu sprechen).

Ein erstes Flipflop nimmt bei einer positiven Flanke die Eingangswerte entgegen und speichert diese zwischen. Dieses ist das Haupt-Flipflop (Main).

Ein zweites Flipflop ist direkt an die Ausgänge des Haupt-Flipflops geschaltet, erhält jedoch ein negiertes Taktsignal: es leitet die Werte des Haupt-Flipflops bei einer fallenden Flanke weiter und unterstützt das main Flipflop - man kann es daher als steward oder servant bezeichnen.

Der große Vorteil dieser Art Flipflops ist, dass der Eingabe- und Verarbeitungsprozess zeitlich von dem Ausgabeprozess der Flipflops getrennt wird. Dadurch lassen sich Nebenwirkungen durch asynchrones und signallaufzeitabhängiges Verhalten minimieren.

Auch MS-Flipflops haben ein eigenes Schaltzeichen: die Ausgabe bei einer fallenden Flanke wird durch eine Flankendarstellung an den Ausgängen notiert:

Übungsaufgabe: Wir kommen zur Königsdisziplin: Welchen Zustand hat das erste (main) und zweite (steward) Flipflop in der obigen Schaltung an den jeweiligen Ausgängen Q bei folgenden Eingangssignalen?

Bei der folgenden Lösung wurden Eingangssignale, die eine Zustandsänderung hervorrufen, gesondert markiert:

Nächster Artikel

Nach den Grundlagen zu Flipflopschaltungen und der Taktsteuerung geht es im folgenden Artikel um D-/T-/JK-Flipflops.

Links und weitere Informationen

Die Beispieldatei mit den aufgebauten Flipflopschaltungen (in der Software Logisim Evolution) findet sich hier (link)

Hinweis zur Nachnutzung als Open Educational Resource (OER)

Dieser Artikel und seine Texte, Bilder, Grafiken, Code und sonstiger Inhalt sind - sofern nicht anders angegeben - lizenziert unter CC BY 4.0. Nennung gemäß TULLU-Regel bitte wie folgt: “Taktgesteuerte Flipflops” von oer-informatik.de (H. Stein), Lizenz: CC BY 4.0. Der Artikel wurde unter https://oer-informatik.de/flipflops_taktgesteuert veröffentlicht, die Quelltexte sind in weiterverarbeitbarer Form verfügbar im Repository unter https://gitlab.com/oer-informatik/digitaltechnik. Stand: 06.01.2025.

[Kommentare zum Artikel lesen, schreiben] / [Artikel teilen] / [gitlab-Issue zum Artikel schreiben]